异步时序逻辑是电路的工作节奏不一致,不存在单一的主控时钟,主要是用于产生地址译码器、FIFO和异步RAM的读写控制信号脉冲。时序逻辑是指输出不但和当前输入的逻辑值有关,而且和在此以前曾经输入过的逻辑值有关的逻辑系统。

时序逻辑是指输出不但和当前输入的逻辑值有关,而且和在此以前曾经输入过的逻辑值有关的逻辑系统。异步时序逻辑是电路的工作节奏不一致,不存在单一的主控时钟,主要是用于产生地址译码器、FIFO 和异步 RAM 的读写控制信号脉冲。除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件;电路状态改变完全有外部输入的变化直接引起。由于异步电路没有统一的时钟,状态变化的时刻是不稳定的,通常输入信号只在电路处于稳定状态时才发生变化。

简介

异步时序逻辑,一般也称作异步时序逻辑电路,没有统一的时钟,各级触发器的状态变化不是在统一的时钟作用下完成的(触发器的状态变化不是同时发生的),电路的状态是直接由输入信号决定,电路结构简单,但是速度慢,随着位数的增加,计数器从接受计数脉冲到稳定状态的建立,时延也大大增加。异步时序逻辑是循序逻辑的普遍本质,但是由于它的弹性关系,他也是设计上困难度最高的。最基本的储存元件是锁存器。锁存器可以在任何时间改变它的状态,依照其他的锁存器信号的变动,他们新的状态就会被产生出来。异步电路的复杂度随着逻辑门的增加,而复杂性也快速的增加,因此他们大部分仅仅使用在小的应用。然而,计算机辅助设计工具渐渐的可以简化这些工作,允许更复杂的设计。也可能建造出混合的电路,包含有同步的触发器和异步的锁存器(它们都是双稳态元件)。异步时序逻辑电路的特点:

所有触发器的 CP 端并没有完全连接在一起;

不是所有触发器状态的变化都与外接时钟脉冲同步;

有时钟信号的触发器才需要用特性方程计算次态,而没有时钟信号的触发器将保持原来的状态不变。

类别

异步时序逻辑电路根据输入信号的形式不同分为脉冲异步时序逻辑电路和电平异步时序逻辑电路。脉冲异步时序逻辑电路主要由触发器组成,与同步时序逻辑电路相似,不同之处在于触发器中的时钟不统一,分析方法和同步时序逻辑电路的方法也基本相同。

电平异步时序逻辑电路主要由带反馈的组合延迟单元电路组成,其分析方法和前者完全不同,主要用状态流程表和时间图的分析方法。设计电平异步时序电路一般步骤如下:建立原始流程表,此时,不但要确定各种输入下的稳态,还需确定各稳态之间转换所需要的过渡状态;对原始流程表进行简化;进行状态分配,由于在最简流程表中存在不稳定状态,分配时,不仅力求电路最简,还要避免造成误动作的临界竞争;求出表征次态和输出的 Y—Z 矩阵;用 Y—Z 矩阵画出逻辑图,此时,必须检查和消除各种可能出现的险态。对已有的电平异步时序电路分析是上述设计步骤的逆过程。

电平异步时序逻辑电路的特点是:电路的状态改变是由输入信号电位的变化直接引起的,而脉冲异步时序电路状态的改变是由于输入脉冲信号的边沿(上升沿或者下降沿);电路的二次状态和激励状态仅仅相差一个时间延迟,即二次状态是激励状态延时后的再现;输入信号的一次变化可能引起二次状态多次变化;电路中存在稳态和非稳态。

竞争和险态

时序电路中状态之间转换存在着过渡过程,也即存在着非稳态。①竞争。电路在过渡过程中存在着一个以上的非稳定状态变量,若电路所趋向的最终稳定状态与状态变量的变化次序有关,则称电路中的竞争是临界的,否则是非临界的。临界竞争会使电路的输出结果不确定。可以在组合电路部分中插入可控制的时延或者通过适当的状态赋值来消除临界竞争。②险态。当开关电路的两个输入处于不同的逻辑状态,并同时向相反的逻辑状态变化时,则称此电路有竞争存在。如果由于竞争,在输出端出现尖峰(干扰),则称此电路具有险态。险态在组合电路和时序电路中都可能发生,而对电平异步时序电路有严重影响。为了消除险态,可在状态变量的反馈回路中插入时延单元,使输入变量变化完成后,再使状态变量产生变化。

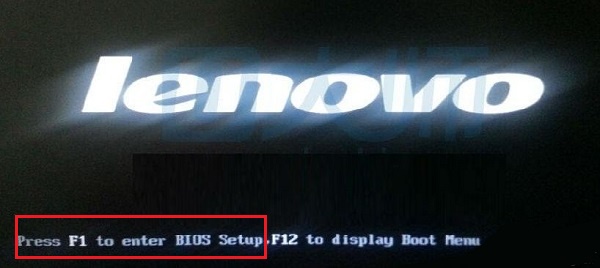

同步、异步时序逻辑电路分析异同

同步时序电路中所有存储元件都在时钟脉冲 CP 的统一控制下,用触发器作为存储元件。几乎所有的时序逻辑都是“同步逻辑”:有一个“时钟”信号,所有的内部内存(’内部状态’)只会在时钟的边沿时候改变。在时序逻辑中最基本的储存元件是触发器。

同步逻辑最主要的优点是它很简单。每一个电路里的运算必须要在时钟的两个脉冲之间固定的间隔内完成,称为一个 ‘时钟周期’。只有在这个条件满足下(不考虑其他的某些细节),电路才能保证是可靠的。

同:均先依据电路图得到电路描述的三大方程,即驱动(激励)方程、状态方程(组)、输出方程,然后依据三大方程得出描述电路逻辑功能的三大图表(通常时序图为实验或仿真条件下的观察图像,分析时可略),最后依据图表描述电路的逻辑功能。

异:异步时序逻辑电路分析时,还需考略各触发器的时钟信号,当某触发器时钟有效信号到来时,该触发器状态按状态方程进行改变,而无时钟有效信号到来时,该触发器状态将保持原有的状态不变。